GIC700组件

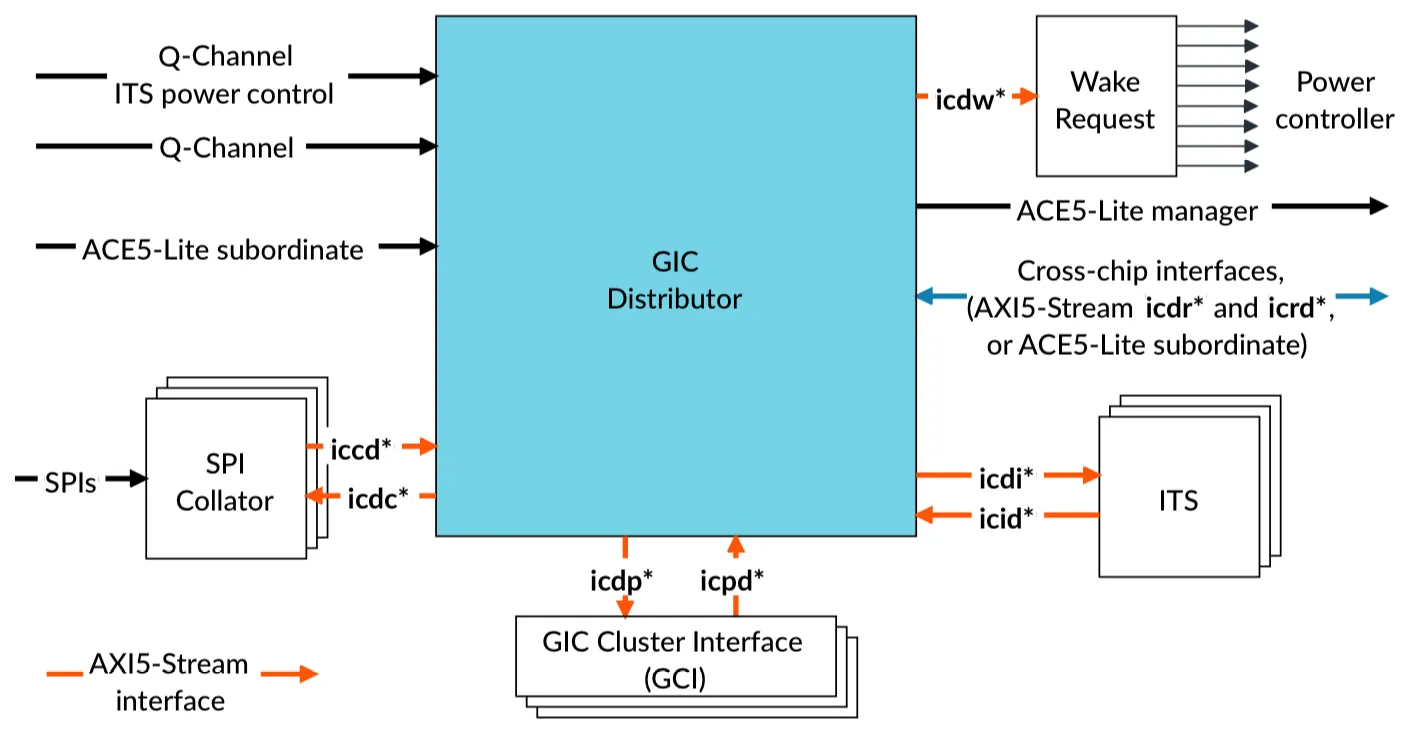

GIC700包含了几个重要的组件,它们使用一个内部的GIC互联,用于在不同的组件之间使用AXI5-Stream接口进行路由。

1. Distributor(GICD)

gicd是GIC700中所有组件之间的主要通信节点。它作为SPI的管理者以及维护LPI的cache,并且与其它chip上的GIC700组件进行通信。当支持GICv4.1架构时,它还作为vPE的管理者。

gicd是GIC的主要中心,它实现了大部分GICv4.1架构,包括:

- SPI的编程、转发和优先级

- 缓存和转发LPI

- SGI路由和转发

- 当配置为支持GICv4.1时,支持vSGI转发和路由

- 当GIC配置为支持GICv4.1时,管理和控制vPE和驻留

- 所有寄存器的编程接口,除了GITS_TRANSLATER

- 核和gicr的电源控制

gicd支持不带gci的配置。此选项适用于具有中断I/O的中央集线器设备和向远程计算芯片提供中断的系统。这些系统还支持具有LPI但没有ITSs的场景,其中LPI仅在中央集线器设备上生成。软件可以读取GICD_CFGID.NITS来确定是否没有本地ITS存在。如果gicd没有GCI,那么它会包括GICD_VCFGBASER和GICD_VSLEEPR寄存器。

如果系统中包含一个没有GCI的chip,那么该架构不支持1 of N类型的SPIs。

1.1 Distributor AXI5-Stream interface

GIC700使用AXI5-Stream接口来与其它组件进行通信

这个接口是:

- 完全被信任的

- ic<xy>tready xy可以为cd,dc,pd,dp,id,di,rd,dr或dw

无论使用何种互连,都不能在端点之间重新排序数据包,例如,在gicd和单个gicr之间。数据包绝不能交错。

信用的数量,或未完成的事务处理能力,在所有的AXI5-Stream接口上是固定的,但有以下例外:

- 对于使用GITS_OPR寄存器锁定在ITS缓存中的事务,可以使用number_int_credit(1-16)和number_ll_int_credit(0-4)配置参数来设置从每个ITS到GICD的未完成lpi的数量。

- 从一个chip传输到另一个chip上,未完成的LPIs或vLPIs的总数量,可以使用lpi_cc_tokens(1-8)配置参数来设置

- 从一个chip传输到另一个chip上,未完成的SGI和vSGI的总数量,可以使用sgi_cc_tokens(1-8)、vsgi_cc_tokens(1-8)配置参数来设置

- GICD_FCTLR3可以对跨片AXI5-Stream接口的事务数量设置一个总体限制。如果跨芯片接口配置为使用ACE5-Lite,则软件可以使用GICD_CCCTLR来限制事务的数量。

AXI5-Stream输入接口

| Bus | Destination | width(bit) | ictid |

|---|---|---|---|

| ICID | ITS to gicd | 16 or 64 | ITS number |

| ICPD | gicr to gicd | 16 or 32 or 64 | gicr number |

| ICCD | spi collator to gicd | 16 | spi collator number |

| ICRD | remote chip to gicd | 64 | 0 |

AXI5-Stream输出接口

| Bus | Destination | width(bit) | ictid |

|---|---|---|---|

| ICDI | gicd to ITS | 16 or 64 | ITS number |

| ICPD | gicd to gicr | 16 or 32 or 64 | gicr number |

| ICDC | gicd to SPI collator | 16 | SPI collator number |

| ICDR | gicd to remote chip | 64 | programmed value |

| ICDW | gicd to wake request block | 16 | - |

1.2 Distributor ACE5-Lite subordinate interface

GIC700的gicd组件上的AMBA ACE-Lite从属端口提供对除GITS_TRANSLATER寄存器外的整个寄存器映射的访问。接口支持64位、128位、256位和512位数据宽度。

GIC700只接受编程模型中显示的每个寄存器大小的单拍访问

当GIC700是一个没有MSI-64支持的单片配置时,gicd和ITS都共享一个ACE5-Lite从属端口,并且ITS转换的DeviceID从awuser_s[did_width−1:0]信号中获取。

1.3 Distributor ACE5-Lite manager interface

gicd使用AMBA ACE5-Lite管理器接口来访问分配给GIC的所有pending表、property表和translation表。此接口仅在支持lpi时出现,或GIC具有ACE5-Lite跨芯片接口,或两者兼而有之。

接口的宽度可以配置为64位、128位、256位和512位。

对于多芯片配置,如果GIC具有ACE5-Lite跨芯片接口,则使用gicd ACE5-Lite管理器接口进行跨芯片通信。系统必须保证来自gicd ACE5-Lite管理器接口的流量能够畅通无阻地到达系统中其他gicd的跨芯片ACE5-Lite从属接口,而不会阻塞对内存的访问。

1.4 Distributor Q-Channels

有一个Q-Channel用于时钟门控GIC700的gicd。当gicd忙于处理中断时,Q-Channel接口拒绝访问。

gicd也有一个单独的Q-Channel,可以对每个配置的ITS进行功率控制。当GITS_CTLR.Quiescent置1时,GIC只接受低功耗请求。如果设置了Quiescent位,则q通道qacceptn_its_信号assert,并且GIC保证到相关ITS的总线在两个方向上都是空闲的,并且ITS可以下电。要执行LPI唤醒功能,可以使用GITS_FCTLR.PWE,在ITS仍处于活动状态并能够转换中断时禁用总线。如果总线被禁用,那么当相应的ITS上的qactive_gicd信号assert时,系统必须重新启用总线并对GICD进行编程,使其准备好接收lpi。系统必须将qactive_gicd信号路由到电源控制器,并执行以下行为:

- 上电GICD

- 恢复GICD程序状态

- 打开GICD上相关的ITS q通道,允许ITS继续进行

由于qactive输出信号包括组合输入和异步输入,因此必须将qactive视为异步输出。

1.5 Distributor P-Channel

p通道用于GIC700的gicd电源控制。

p通道只存在于多芯片配置中。它用于安全地将gicd与其他芯片隔离,以允许保存和恢复其寄存器状态。

2. GIC Cluster interface(GCI/GICR)

GIC集群接口(GCI)负责与其相关的cluster里的核的ppi和sgi。

GCI具有以下功能:

- 维护SGI和PPI的规划

- 监控PPI信号线,如果需要可以用于同步PPI信号线

- 对SGIs和PPIs还有从gicd发送来的中断进行优先级排序,并将其转发给核

- 维护GIC stream 协议,并且与cluster进行交互

在一个配置中可以有多个GCI,并且可以根据系统调整它们的大小。例如,如果有两个8核cluster,那么可以在每个cluster旁边放置一个GCI。可以为每个cluster使用一个GCI,以减少PPI接线,并使GCI能够随核一起断电,从而节省额外的电力。另外,对于小型系统,将所有内核组合到一个GCI中可能是最佳解决方案。

GCI (GICR)寄存器通过个gicd的ACE5-Lite从属接口编程。gicd还包含体系结构中LPI功能。

2.1 GCI GIC Stream Protocol interface

GIC流协议接口,也称为GIC流接口,使用GIC流协议将中断和响应传递到每个核心内部的CPU接口。

| signal | description |

|---|---|

| iri | 下行接口信号。GCI是发送方,CPU interface是接收方 |

| icc | 上行接口信号。CPU interface是发送方,GCI是接收方 |

| iritdest | GCI使用该信号将数据包定向到cluster中的一个core |

| icctid | cluster使用这个信号表明是cluster中哪一个core发送的数据包 |

| iritwakeup | GCI使用该信号表明它想要发送一个消息给cluster中的一个CPU interface |

| icctwakeup | cluster使用该信号表明它想要发送一个消息给GCI |

2.2 GCI Q-Channel

GCI有一个单一的q通道接口,用于确保GCI可以安全地分层进行时钟门控。

如果GCI繁忙,正在积极处理中断或向上游或下游发送消息,则Q-Channel通过断言qdeny信号来拒绝它在qreqn信号上接收到的quiescence请求。

qreqn输入信号在GCI内部同步。qactive信号直接连接到PPI线,必须被视为异步输出。

2.3 GCI PPI signals

对于每个核,GIC-700支持16、32或48个ppi和同步输出返回线。对于共享GCI的所有核,ppi和返回线的数量必须相同。

与以前的Arm GIC实现一样,电平敏感PPI信号默认为active-LOW。但是,单个PPI信号可以使用以下参数进行反转和同步:

- GIC700_ < usrcfg > PPI < ppi_id > _ < cpu_number > _ < ppi_number > _

- GIC700_ < usrcfg > PPI < ppi_id > _ < cpu_number > _ < ppi_number > _

每个ppi信号在同步器或捕获触发器之后都有一个相应的ppir信号。这些ppir信号可用于为跨时钟域的边缘触发中断创建脉冲扩展器。GIC700PPI<ppi_id><cpu_number><ppi_number>参数也反转ppi_r信号。

如果计划使用边缘触发ppi并使用q通道分层地对GCI进行时钟门,那么必须包括脉冲扩展器。脉冲扩展器确保在时钟重新启动时不会错过中断。

3. Interrupt Translation Service(ITS)

中断转换服务(ITS)提供了一种软件机制,用于将基于消息的中断转换为lpi或vlpi。

当GIC配置了可选旁路开关和可选直连端口时,ITS模块如下图所示。

ITS是GICv3和GICv4中断转换服务的具体实现。ITS将MSI请求转换为所需的LPI和目标。它还有一组用于管理LPI的命令,用于核心电源管理和负载平衡。

ITS的一个主要用途是转换来自PCIe根复合体(RC)的MSI/MSIx消息。

为了完成转换,必须为ITS提供一个派生自PCIe RequestorID的DeviceID。为了减少DeviceID传输的距离,并在RC之间实现更好的分区,ITS最好放置在RC旁边。为了便于集成,ITS有一个可选的旁路开关。如果没有配置bypass开关,ACE5-Lite从端口直接与ITS相连。

3.1 ITS ACE5-Lite subordinate interface

ITS AMBA ACE5-Lite从属接口具有64位,128位,256位或512位的可配置数据宽度。

ITS ACE5-Lite从属端口只包含GITS_TRANSLATER寄存器。

如果选择bypass开关配置选项,则端口接受所有ACE5-Lite流量,并根据target_address[ADDR_WIDTH−17:0]ITS基址绑定设置的地址匹配过滤访问ITS。如果没有旁路开关,地址的上位(16及以上)将被忽略,系统地址解码器必须确保只有相关的ITS写操作才能到达ITS。无论是否选择bypass开关,写ITS从属接口必须将awaddr[16:0]信号置为0x0040。

ACE5-Lite从属接口忽略所有的awatop、asnoop、acache、adomain和aprot信号信息,而不是过滤非内存事务(如原子和缓存维护操作),以确保它以符合协议的方式进行响应。

GIC700使用wstrb信号来确定事务的大小。GIC拒绝那些没有形成一个连续块的事务,该块的地址与事务的结果大小一致。

为了生成LPI, ITS需要DeviceID。对于PCIe, DeviceID派生自RequestorID。

GIC700支持两种不同的方法来获得ACE5-Lite从属接口派生DeviceID:

- 当使用MSI-64配置参数时,对GITS_TRANSLATER的写被转换为64位的对未映射的系统地址的访问,而DeviceID被转换为访问的前32bits。在这种情况下,只接受突发长度为1的64位ACE5-Lite写操作。

- 当不使用MSI-64时,在寄存器访问的地址(AW)阶段,DeviceID在awuser_s[did_width−1:0]信号上传输。在这种情况下,突发长度为1,32位或16位写入才被接受。

这两种模式不能在单个ITS上混合。DeviceID必须使用恶意软件无法欺骗的方法传输。

ITS还支持直接MSI接口,其中MSI通过AXI5-Stream接口直接发送到ITS。该接口可以与ACE5-Lite的从属接口一起配置,也可以代替其配置。

3.2 AMBA bus properties,ITS

AMBA协议定义了多种属性类型,用于指示设备的功能。

3.3 ITS AXI5-Stream interface

ITS的AXI5-Stream接口是一个16位或64位宽度的双向接口,用于ITS和同一芯片上的gicd之间的通信。

典型的分布式系统是16位宽。当使用预先存在的宽互连时,64位宽的接口允许有效地打包消息。

该接口是完全可信的,因此可以接受所有消息,而不依赖于任何其他端口。

3.4 MSI delivery interface

MSI传递接口是一个双向的AXI5-Stream接口,用于将MSI传递到ITS进行转换。

msitdata信号的数据格式为{DeviceID[31:0], EventID[31:0]}。当ITS接受请求时,它将msirtvalid信号设置为HIGH。

GIC对DeviceID和EventID的全部32位进行解码。高于配置宽度的位必须为零,否则GIC会产生超出范围的错误,并且不会发生预期的转换。

ITS接收到的msitid信号值,在msitdest信号上发送出去。这种行为允许多个源使用标准的AXI5-Stream基础结构连接到ITS。

如果ITS或gicd资源变得繁忙,MSI交付接口可以应用回压,并且可以依赖于gicd的ACE-Lite管理器接口,用于读和写。

4. MSI-64 Encapsulator

MSI-64 Encapsulator通过将DeviceID合并到数据总线上,以便写入GITS_TRANSLATER寄存器,从而减少了系统布线。

MSI-64 Encapsulator检测以GITS_TRANSLATER寄存器的页地址为目标的翻译,这是由msi_translator_page绑定信号设置的。然后,它将访问转换为64位写,awdeviceid信号值位于数据的上32位,并将它们重新定位为msi64_translator_page信号。这避免了必须使用连接将DeviceID传输到GITS_TRANSLATER寄存器以进行翻译。

MSI-64 Encapsulator有一个ACE5-Lite subordinate接口和ACE5-Lite manager接口

-

MSI-64 ACE5-Lite subordinate interface with awdeviceid:

该接口是一个完整的ACE5-Lite附属接口,带有一个额外的awdeviceid输入信号,该信号是有效的,并且必须与awvalid信号保持稳定。

-

MSI-64 ACE5-Lite manager interface:

gai 接口是一个完整的ACE5-Lite管理接口。

5. SPI Collator

SPI Collator将SPIs信号线转换成消息,并将其发送给gicd。一个GIC中最多可存在32个SPI collators。

单个SPI可以同步到SPI Collator中,或者SPI Collator可以与中断源以及同步到gicd的消息放在同一个时钟域中。

将SPI Collators放置在始终开启且远离gicd的时钟域中,可以更好地节省电力,因为gicd可以分层进行时钟门控。

如果一个GIC配置使用多个SPI collator,那么必须设置SPI_BASE值,这样SPI线就不会重叠。

SPI_BASE值控制SPI排序器的基址,它可以通过使用SPI_BASE参数或SPI_BASE信号来设置。在配置过程中决定是否使用参数或信号来设置芯片上所有SPI collator的基址。

例如,如果芯片使用参数来设置其三个SPI排序器的基址,则SPI_BASE参数可以设置为:

- SPI Collator有64线——SPI_BASE 0

- SPI Collator与32线——SPI_BASE 64

- SPI Collator与128线——SPI_BASE 96

SPI Collators不需要支持32线的倍数。

6. Wake Request

唤醒请求模块将axis5 - stream唤醒请求转换为每个核的一个wake_request信号。每个wake_request信号连接到系统电源控制器。

wake_request信号会在以下情况下唤醒处于下电状态的核:

- 针对指定核的中断处于pending状态

- 当GICD_CTLR.E1NWF字段为1时,一个1 of N类型的SPI以该核为目标

GIC700是不知道核是上电还是下电的。它只知道软件是否能在AXI5-Stream接口上发送事务。因此wake_request信号在核上电之后会保持asserted。当软件将GICR_WAKER.Processorsleep清除之后,wake_request信号才会deassert,然后GIC700会清除GICR_WAKER.ChildrenAsleep位。

当GICR_WAKER.Processorsleep被置位,如果有一个中断处于pending状态,该中断要么以指定的核作为目标,要么是1 of N模式,那么wake_request信号会在下电时assert。电源控制器在核下电之前会忽略wake_request信号。

只有当以下情况下wake_request信号会从assert转换为deassert:

- gicd退出reset状态,它会发送一个clear消息给wake request模块

- 核处于唤醒状态并且软件清除GICR_WAKER.Processorsleep位。它表明核可以与GIC进行交互了

- wake_request模块复位。如果该模块进行复位,那么gicd必须也进行复位

7. Top-level