FPGA故障注入测试软件使用指南

有数字芯片之母别称的FPGA,是国内在半导体行业率先取得重大突破的细分赛道,正迎来技术和市场形成共振的黄金发展期。

国内拥有最多的应用设计工程师与新兴从业人员,但到目前为止,还没有一款位流级别的专用EDA软件,服务用户日常应用开发所需的调试验证工作。

第一大厂商赛灵思,虽然早在二十年前,为高性能的SRAM FPGA能够应用在太空环境,就联合NASA推出的大型故障注入设备(XCRT),已成为包括火星车在内的诸多重大航天工程的基石,但只为境内联盟成员提供服务;

2012年,因应先进制程工艺(28nm)器件,芯片硬件电路对单粒子效应(SEU)更为敏感,用FPGA构造的产品更为“脆弱”的需求趋势,2012年正式将SEM IP核,作为FPGA在任务关键、安全关键等行业用户的首选解决方案。

包括航空、军工、汽车电子、医疗健康、数据中心、网络通信设备等的故障注入解决方案。

宣传语是“Error injection is a VERY Powerful tool”,就像自己就可以做“辐照”实验,但是更精准、功能更强大。

用户对设计进行非破坏性的日常故障注入测试,能够为产品的最终部署使用,注入更多信心。

理想丰满,现实骨感。FPGA应用开发难度大,全球用户都感同身受,应用设计不易,调试验证难度大,能够在真实硬件环境下对整个系统进行故障注入测试,难度系数再升两个等级。

有技术研发实力的申请发明专利,如军工巨头雷神技术2020年的“Fault injection can replace the beam test or mitigate risk of a failed beam test”;国内在体系结构研究走在最前沿的、也是FPGA应用研究最深之一的国防科大,2021年发表的《利用整帧翻转的SRAM型FPGA故障注入加速算法》等。

虽然赛灵思的故障注入解决方案已推出二十余年,要么是服务的不可获得性(XCRT),能获得甚至免费的SEM IP,又实在难以使用,把用工具直接提供的数据,做成了各个行业用户的学术论文。

从早年Jbits年代院士门生的博士毕业大论文,到现在各类政府资金资助项目的结题结项“学术论文”,汗牛不充栋,数量种类也是足够丰富。

调试是自动化最后的堡垒,数据是调试的生命线,而代表FPGA最先进调试能力的硬件辅助验证两大专用设备,配置的要么是太臃肿的复杂大软件,要不就是技术曲线过于陡峭,需要额外专业培训才能使用的昂贵EDA工具。

当软件早已不再只是单纯的工具,而是成为综合性的服务,在AI时代更是以成果为交付物的现在,我们希望全自主开发的forgedaFX软件,能成为帮助用户加快产品开发、提升质量的必备生产力工具:

轻量便捷、正版且花费不多

历经近十年的迭代优化,技术水平居于行业领先水平,化繁为简,事半功倍:Dancing with More People。

FPGA本身是建立在芯片基础上的软件生意:为用户节省时间,为芯片厂商节省人力成本支出! 简单的直接用EDA工具自动完成;复杂疑难问题,用EDA工具的自动化能力,辅助工程师完成。

本使用指南完整版本等更多产品资料,可通网站gitee.com/forgeda直接获取查阅,链接地址FPGA故障注入工具

以下为正文

非破坏性故障测试的主要目的,在于获取用于计算可靠性指标的“基础数据”,用来快速验证多模冗余、配置刷新等设计加固措施有效性等。

即便在非常特殊的空间领域应用场景,也已成为进入到物理故障注入前的最后确认测试环节,所需的事前准备工作。可避免如果直接进行“行业黄金法则”的破坏性辐照试验,因一次不成功造成的巨大成本风险。

forgedaFX软件的工作主界面,包含两大核心功能:第一部分是业内独创的位流数据分析,是用户在真实硬件环境下,实现对实物系统进行故障注入操作的基础;

第二部分是通过软件提供的故障注入数据库,对任意DUT快速搭建SEU 硬件仿真环境:由用户根据自己的测试向量,通过三种方式进行故障注入,并统计关键位(Critical bits)数量,包括可在刷新后恢复正常功能的Bits,以及最重要的持续性故障点(Persistent Bits)。

Persistent Bits也被称为不可恢复异常比特位(Unrecoverable Critical Bits)——不能通过定时刷新修复,也是卫星等行业在地面故障注入试验需要重点关注、着重评估并优化改进的比特位。

只能通过系统重启方式,才能恢复正常功能。

具体地,用户可通过位流数据分析和故障注入测试,统计设计“关键位”数量,获得降级因子 ε,从而表征设计易受SEU影响的程度,即随机发生的配置编程点翻转导致系统功能错误的概率。

使用上述降级因子数据,易于对三模冗余设计等加固措施的有效性进行量化评估;计算动态翻转截面数据,用于失效率等可靠性指标的估算。

降级因子的值越小,说明SEU翻转导致系统设计故障的概率越低。相应的,可靠性就越高,系统就越健壮。

以KU040 FPGA上的复杂处理器系统加固设计为例,通过计算降级因子,如下图所示:

用户只需比较两个降级因子,便可知采用TMR加固后的设计,与之前的设计相比,系统健壮性提升14.87倍。

如果您需要任何使用帮助或问题建议,可发送电子邮件至viewall@forgeda.com,我们乐于为您详尽解答。

forgedaFX软件与FPGA芯片型号绑定使用,并以其作为软件产品具体型号的命名规则。以本指南使用的forgedaFX-325软件为例,可支持两大类别、共51款Xilinx 7K325T芯片(详见第七章的FPGA具体型号列表)。

如您使用的是forgedaFX-690软件,可支持赛灵思公司第七代的所有Virtex 690T芯片,共32款型号。其中,通用型24款,高等级芯片8款。如您使用的是forgedaFX-060软件,则支持的是赛灵思更先进工艺(UltraScale)的全部KU060芯片,包括通用性XCKU(18)、高等级XQ(4)和宇航级XQR(1),共23款具体型号。

初识forgedaFX

forgedaFX软件为您提供了一个友好、简洁的使用界面,启动后显示的全景GUI,主要功能已在主菜单栏清晰列明。

左侧是FPGA芯片基本信息以及CRAM配置存储器数据展示窗口、右边为项目配置信息,控制台消息输出窗口,共7个区域。

FPGA芯片型号、当前项目名称、工作目录等信息自动显示在主界面。

① 主菜单栏

包括【项目】、【分析】、【查看】、【测试】、【帮助】等功能,您可通过选择相应的菜单,完成所需的操作:

【项目】

用于故障注入测试项目的创建、导入、关闭以及软件退出操作

【分析】

对FPGA位流数据进行自动分析,智能过滤与设计无关的冗余编程点,快速创建故障注入测试数据库文件(Fault Injection DB File)。

【查看】

提供“风险地图”、“编程点记录”、以及“概要信息”三种方式,便于用户查看位流数据分析结果。

【测试】

用于对DUT应用设计有关的编程点进行SEU故障注入操作。

【帮助】

可用于打开forgedaFX软件用户使用指南(本文档)、显示软件版本信息等。

除了选择以上菜单项来执行操作,您也可通过“Alt+快捷键”方式,直接运行要使用的功能,如直接用“Alt+P”快捷键,选择【项目】菜单。

② 工具栏

显示快捷工具图标,执行以下常用操作:

③ 当前项目信息显示区域

位于界面右上方,显示当前测试项目名称、工作目录,目标FPGA型号,以及FPGA应用设计对应的.dcp文件。

④ DUT信息显示区域

显示目标FPGA芯片基本信息,以及在分析后得到的“配置存储器数据规模”、“故障注入数据库中的编程点总数”。

⑤ 控制台消息输出窗口

在数据分析启动后,实时显示当前进程和状态消息

⑥ 进度条窗口

用于表示“程序正处于运行状态”

⑦状态栏

显示当前项目的状态描述信息

技术虽不能直接解决问题,但肯定可以提升效率。

forgedaFX软件的核心能力, 是提供智能化的二进制数据分类标记、过滤等功能,对用户设计有关的测试点集合进行归集,进而在海量配置存储器中,快速过滤大量与用户原生设计无关的冗余测试点,并且这个工作阶段是完全自动化,零门槛。

经过数据分析获得的故障注入数据库文件,是后续故障注入操作的基础。可避免大量无效的冗余点注入,做到有的放矢。与采用无差别的全芯片随机或遍历方式,就直接进行故障注入的常规测试方式相比,可将验证效率至少提升300%以上。

本章将以时钟计数器为样例(详见附录1),介绍如何创建您的第一个故障注入测试项目。

该样例以1/4秒为周期,由时钟计数器驱动LED显示,所有设计文件位于forgedaFX软件的demo/Vivado_counter_demo子目录。

3.1 新建项目

在正式启用软件前,首先创建一个专用空白目录,用于保存和记录在软件工作过程中,新生成的项目文件和测试数据等。

请注意命名规范,不含中文字符、空格符等,以免影响顺畅的使用体验或软件任务报错。

然后启动软件,在主界面工具栏选择“创建新项目”。

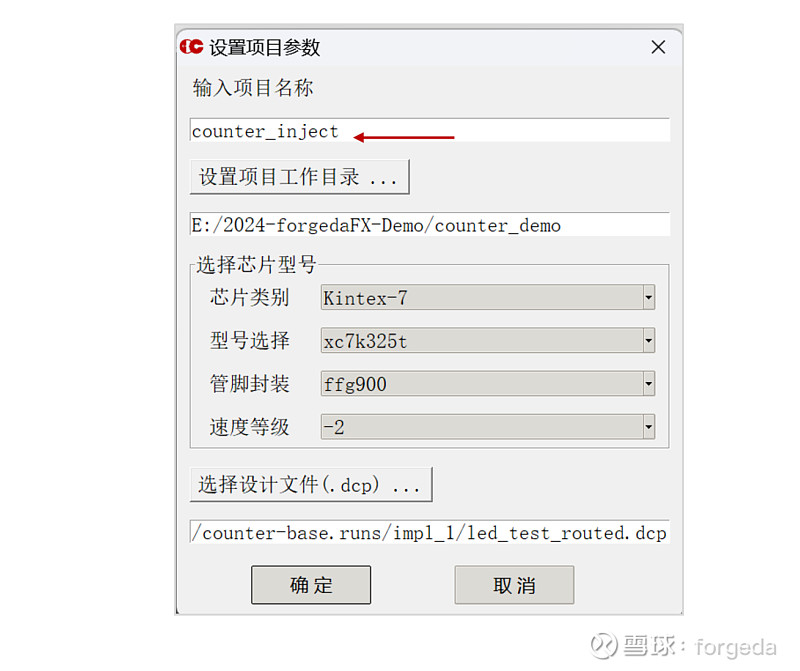

在“项目参数设置”对话框中,分别输入以下信息:

(1) 选择事先已准备好的专用工作目录(即此时无任何内容的空白目录);

(2) 直接在软件界面上命名“项目名称”;

(3) 选择目标FPGA芯片的详细信息(型号、速度等级、管脚封装等);

(4) 选择设计文件.dcp(即设计在布局布线后最终产生的_routed命名文件)。

在本演示样例中,输入的.dcp文件,位于demo/Vivado_counter_demo/

counter-base.runs/impl_1/led_test_routed

Step1

创建专用文件夹(例如,本演示样例名为counter_demo),作为当前项目专用工作目录,用于保存和记录测试文件和结果数据;

在正式启用forgedaFX软件后,数据分析日志、起止时间、故障注入测试结果等项目文件,会自动放置在该“空白”文件夹内,以便于随时查阅或回溯分析。

Step2

在forgedaFX软件主界面工具栏选择“创建新项目”,通过项目参数对话框,对该新项目进行命名(例如,本演示样例将counter_inject作为项目名称)。

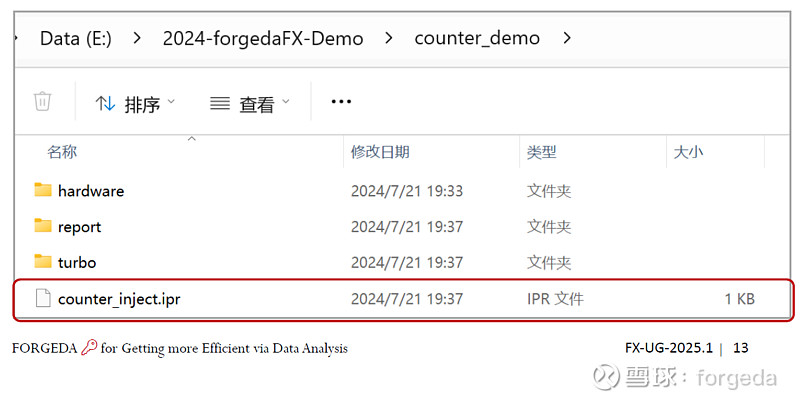

项目参数设置完成,点击“确定”,完成项目创建。

右下角状态栏显示“new project created successfully”提示,表明项目已成功创建。软件界面右上侧将显示您所创建的项目信息,包括:项目名称、项目工作目录、设计文件、FPGA芯片型号,便于您核对检查,确认是否已正确无误。

该步骤完成后,在项目工作目录下,自动产生后缀名为.ipr的项目描述文件(counter_inject.ipr)。该文件作为forgedaFX软件专用的项目描述信息,便于您在后续用于快速导入该测试项目。

3.2 数据分析

项目创建成功之后,启动软件“数据分析”功能。

在运行过程中,界面右侧的控制台消息窗口实时显示当前工作进度,并在右下角状态栏显示“data analysis started”。

进入数据解析阶段,对 FPGA位流数据的处理过程全自动化,无需任何人工干预。

分析所用时间与FPGA芯片规模、应用设计复杂度密切相关,请耐心等待。比如在本样例中,数据分析耗时2分钟,工作速度为每秒钟超过600,000 bits以上。

一旦结束,消息窗口提示“data analysis completed”,在控制台消息窗口显示运行时间以及分析结果。

与此同时,软件界面左侧显示目标FPGA 配置存储器(CRAM)规模,以及用户设计相关位总数(Essential bits),即故障注入数据库(Fault Injection DB)规模。

如上图示,在该样例中,forgedaFX软件从目标器件(7K325T芯片)共计91530240 bits位流规模中,首先识别用于配置硬件电路的CRAM数据(72868672 bits),再过滤筛选与counter硬件电路结构、功能无关的冗余测试编程点,最后精准标记出只与该设计相关的Essential Bits(15114 bits),即FPGA故障注入所用数据。

该数据同时记录在故障注入测试数据库文件中(即图中的result_record.txt)。

分析过程结束,在当前项目工作目录下的report文件夹,产生日志文件biti.log,结果概要文件bits_summary.txt,以及完整的故障注入测试数据库文件result_record.txt,便于查阅。

故障注入测试数据库文件,提供了FPGA芯片内部,与DUT有关的完整配置编程点地址,是后续实现故障注入的基础。

3.3 查看分析结果

在数据分析过程结束之后,forgedaFX软件提供三种方式显示分析结果,可直接在软件工具栏点击对应图标按钮,直接“查看”相关的数据结果。

对数据分析结果的含义,具体解释如下:

3.3.1 编程点记录

选择“查看数据分析结果文件 ”后,软件分页加载并显示配置硬件电路的编程点信息,以列表方式展示各编程点的详细地址,即故障注入测试数据库文件。

也可在创建的工作目录下,点击/report/result_record.txt,查看完整的编程点地址数据。

forgedaFX软件在位流数据分析工作完成后,自动提供与硬件电路设计相关的所有编程点信息,100%全覆盖:具体列明每个编程点的详细物理帧地址、线性逻辑地址、以及详细的位置坐标,数据加载所需时间在10秒左右,如下图示:

各数据栏的详细释义如下:

① 物理帧地址(Physical Frame Address)

FPGA芯片位流数据按帧进行编址,物理帧地址是最直接的编程点寻址方式,也是故障注入操作所需的关键参数之一。在对实物进行故障注入操作时,按照提供的物理帧地址,实现对编程点所在配置帧的读写访问。

例如,上图中序号为1的编程点,物理帧地址为0x00000002,后续可在forgedaFX软件故障注入测试界面,直接作为指定的故障注入地址。

② 逻辑地址(Logic Address)

forgedaFX软件提供的逻辑地址,与芯片原厂商所使用的FPGA芯片编程点专用线性地址格式保持一致,数值是一个长度为9的16进制数。其中,前6位为逻辑帧地址(L),后3位为编程点所在的配置字(W)和配置位序号(B)。

③ 编程点位置

表示编程点在芯片内部的坐标,是物理帧地址、编程点序号的具体化。

④ 逻辑区域序号

forgedaFX软件提供编程点的逻辑区域SLR序号,当SLR序号为0,表示DUT芯片为非堆叠、平面架构的芯片。例如,本使用指南中的具体样例使用的FPGA 为7K-325T,就是非堆叠、只有一个维度的平面架构芯片。

当使用forgedaFX对多维堆叠架构的先进大容量FPGA进行自动解析时,例如目标型号为Kintex UltraScale KU115,当SLR序号值为1时,则表明该编程点位于第二个SLR,以此类推。

3.3.2 风险地图

forgedaFX软件为用户提供应用设计在FPGA芯片内部对应的配置视图,用于展现“ε1(配置资源利用率) ”的物理意义。以数据图谱方式,使得原本处于不可见“黑盒”状态的配置编程点,进行全景展示。

选择“查看编程点风险地图 ”后直接显示如下:

FPGA