蚀刻效果解释

梯形走线的阻抗影响。

直到最近 我认为那些相信矩形痕迹的人和那些相信方波和平坦地球的人一样普遍。不过,最近我开始意识到这并不像我想象的那么清楚,不仅对新手,而且对一般人来说都是如此。在过去的 25 年里,我购买了大量关于 PCB 设计和信号完整性的书籍,阅读大多数行业文献后,您不会知道走线绝不是矩形的。很有趣,对吧?

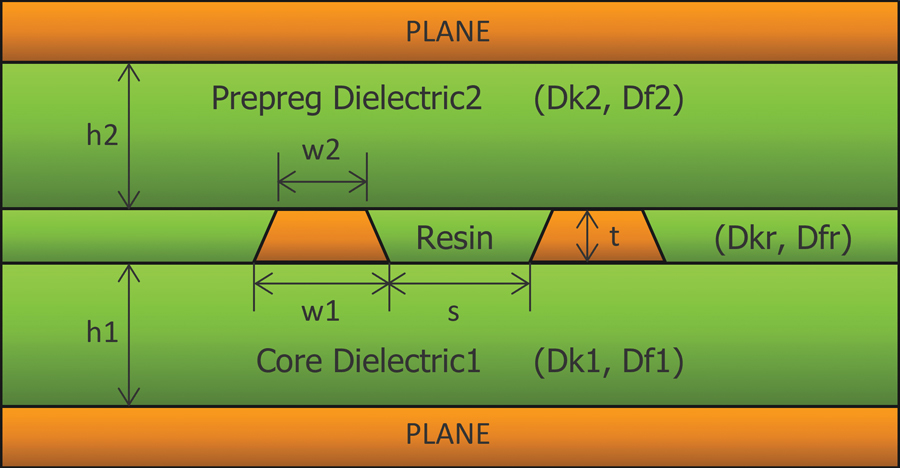

如果您阅读过之前的“Material Matters”专栏,您可能会从我们的 Z 求解器软件中认出以下截面。除其他外,它表明面向核心电介质的走线底部比面向预浸料的走线一侧宽。因此,走线梯形在多层堆叠中同时面向上下。与层号或走线是在电路板的上半部分还是下半部分没有关系。出于这个原因,包括我在内的一些人(但不是所有人)避免使用“top”或“bottom”等术语来表示梯形轨迹。

在图 1 所示的尺寸中,梯形底部的 w1 值是硬件团队和制造商在讨论走线宽度和间距时交换的值。重要的是要知道实际制造的电路板不会有那么多的铜。当痕线从上到下蚀刻时,蚀刻化学品(“蚀刻剂”)与迹线的预浸料侧保持接触的时间比芯侧长。这使得走线的预浸料侧比芯侧窄,并使走线具有梯形横截面。在本专栏中,我们将讨论这种制造现象的原因以及对阻抗的影响。

内层蚀刻。 蚀刻内层包括清洁层压板两侧的铜、涂上光刻胶、曝光光刻胶以创建内层图案、显影光刻胶、蚀刻掉不需要的铜,并去除蚀刻胶。大多数车间都实现了这一过程的自动化,并且化学成分也被自动监测。因此,准确性和可重复性非常好。使用这种工艺,可以蚀刻内层走线,精度为 ±0.5 mils。这种精度控制有助于将阻抗保持在传输线所需的容差范围内。

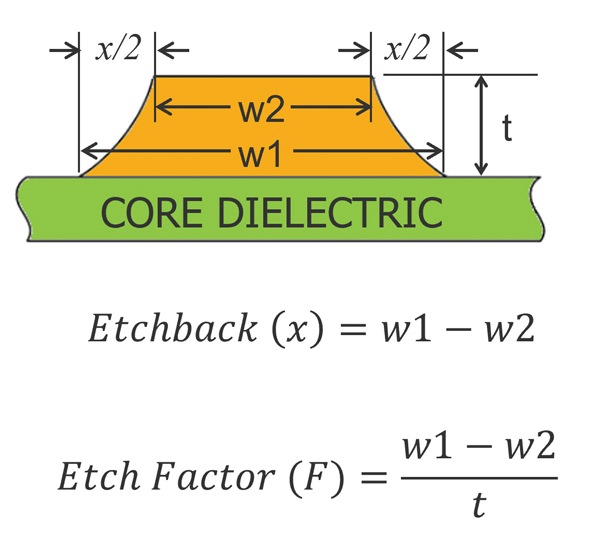

图 1.内层迹线的梯形形状,如带状线横截面所示,其中 w2 比 w1 窄。(图片来自 Z-zero 的 Z 求解器软件)

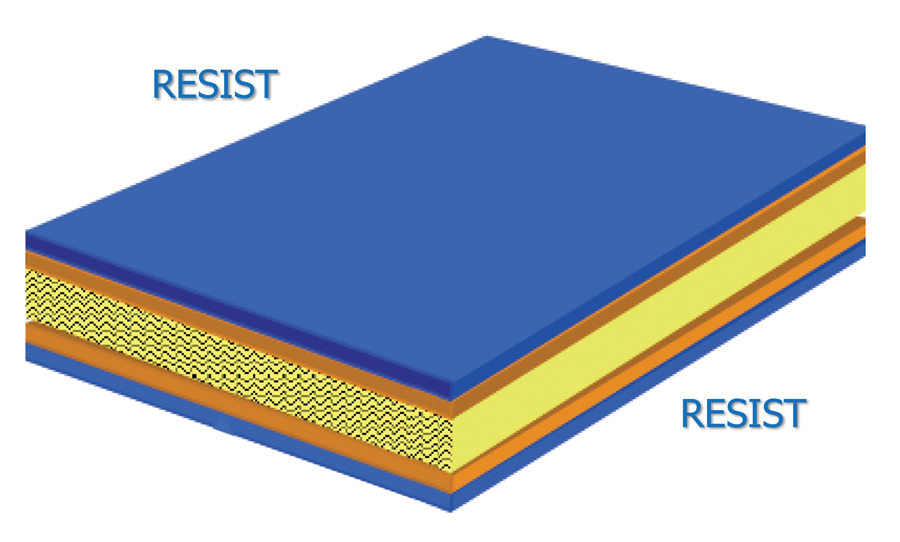

图 2.蓝色光刻胶膜在成像、紫外线曝光和随后的蚀刻之前放置在内层芯的两侧。

清洁磁芯后,图 2 显示了通过加热和压力施加到磁芯金属表面的蓝光敏感膜或可光成像“光刻胶”。该薄膜对紫外线敏感。如果您曾经参观过一家制造车间,处理光刻胶的房间会使用“黄光”来防止光刻胶无意中曝光。滤光片去除了会影响光刻胶涂层的光波长。

该器件的 Gerber、IPC-2581 或 ODB++ 数据用于绘制描绘电路板设计走线和焊盘的薄膜。照相工具或图稿包括铜特征。该胶片用于将图像放置在光刻胶上。

内层薄膜是铜特征的“负片”图像,这意味着处理芯后留下的铜图案对应于薄膜上的透明区域。芯板暴露在高强度紫外线下,用于硬化或“聚合”薄膜光刻胶,从而产生电路图案的图像,类似于幻灯片底片和照片。

然后通过化学“显影剂”处理暴露的芯,该显影剂从未被紫外线硬化的区域去除光刻胶。接下来,从纤芯对铜进行化学蚀刻,在剩余的蓝色干膜光刻胶未覆盖的所有区域。蚀刻后,显影的干膜光刻胶从面板上化学去除,只留下暴露在面板上的铜特征。

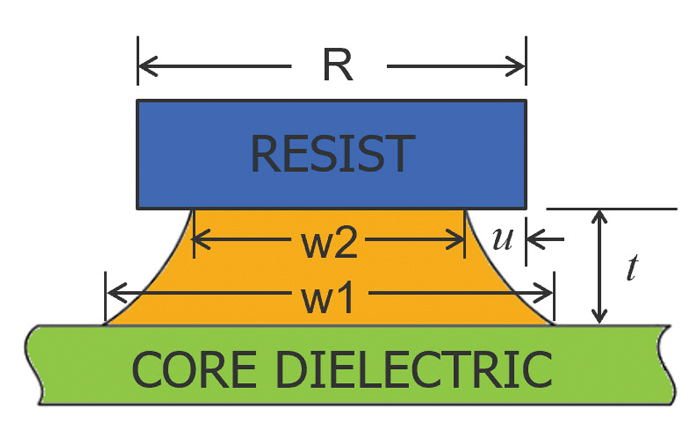

它比我们到目前为止提到的还要微妙。如图 3 所示,走线的实际侧面是弯曲的,蚀刻“底切”位于蓝色光刻胶下方。请记住,w1 是硬件团队和制造商用来描述走线宽度的维度。R 是制造商使用的光刻胶的宽度。抗蚀剂下方的壁架是底切 u。理想情况下,R、w2 和 w1 相等。制造商越接近这一点越好,优秀的制造商会努力实现这一目标。

图 3.走线的实际侧面将是弯曲的,蚀刻 “底切” 位于蓝色光刻胶下方。

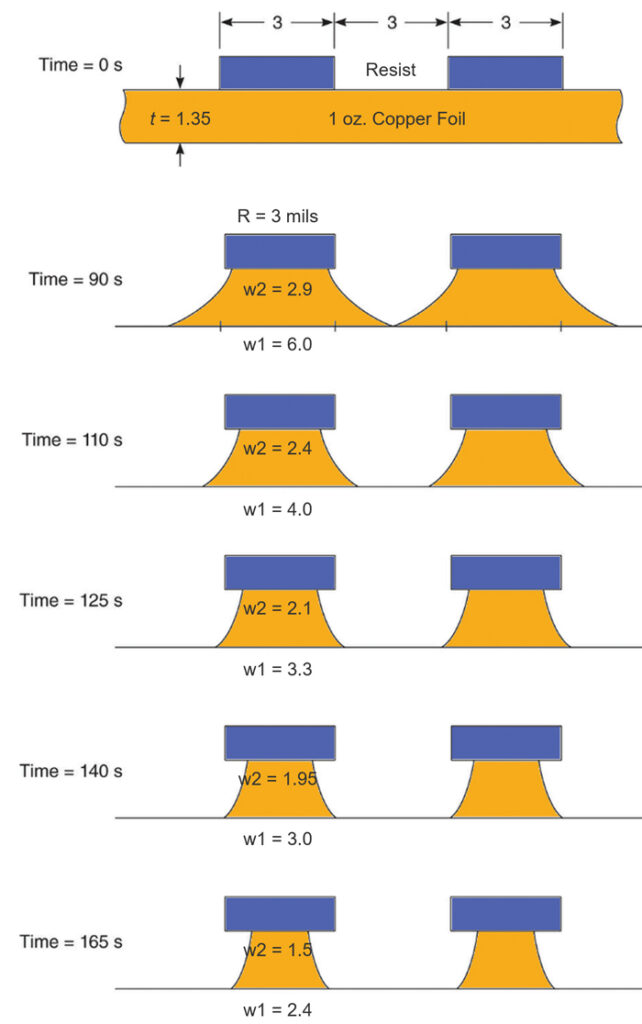

图 4.使用 3 mil 光刻胶,w1 为 3 mil 目标,这些图像显示了铜暴露于蚀刻剂中的时间量决定了铜特征的最终形状和宽度。

光刻胶区域之间的间隙首先均匀地去除,然后逐渐以杯状方式去除,直到走线之间的中心区域突破到暴露的芯电介质,随着蚀刻剂在光刻胶内部和下方工作,随着侧壁通过增加曝光逐渐去除,电介质逐渐打开。铜暴露在蚀刻剂中的时间长短决定了铜特征的最终形状,如图 4 所示。

光刻胶宽度 (R) 等于梯形 (w1) 的底部是理想的蚀刻。在图 4 中,这对应于 140 秒的蚀刻场景。另请注意,如果 R 小于 w1,例如在长达 125 秒的情况下,铜特征或走线被欠刻。在铜暴露在蚀刻剂中 165 秒的情况下,铜被过度蚀刻。这里的时间是针对这个特定示例的,其中氯化铜被用作蚀刻剂,针对 3.0 mil 线和空间图案,在 1 盎司(1.35 mil)铜箔上使用 1.0 mil 光刻胶。

蚀刻因子。从图 3 中的参数来看,蚀刻过程有两种描述性度量:底切和蚀刻因子。底切定义明确。这是顶部宽度减小后光刻胶的平均悬垂。硬件团队真的不需要担心光刻胶的宽度,但“底切”术语和概念很有用。显然,目标是最小化 u 参数。

底切 (u) = R - w2 超过 2

“蚀刻因子”则相当模糊。有些人将其定义为与铜厚度 t 成正比,并且与 w1 和 w2 之间的差异(梯形中的宽度差异)成反比。但根据您与谁交谈,这些关系可能会颠倒或使用不同的参数。

我发现图 5 中所示的关系很直观。如果我们能就这样的定义达成一致,那就太好了,其中 x(“蚀刻因子”)是 w1 和 w2 之间的差值,“蚀刻因子”定义为单位厚度的蚀刻程度。

Fabricator 数据。普通供应商通常分别为 0.5 盎司铜和 0.5 盎司铜保持大约 0.25 密耳的蚀刻背。先进的 PCB 制造商可以将 0.5 盎司铜的这些数字提高到 0.17 密耳,1 盎司铜的 0.45 密耳。

可以说服我改变这种做法,但为了避免出现定义冲突的复杂性,我一直在用百分比来工作,特别是 w2 和 w1 之间的比率(目标是尽可能接近 1.0)。

使用这种方法,先进的 PCB 制造商可能会实现 0.972 的 w2/w1,例如,对于 0.5 盎司的铜。同样,研究表明,先进制造商可以实现 0.925 的 w2/w1。这种方法的局限性在于它假定 w1 的特定值:在本例中为 6 mils。

电镀层。我讨厌打开另一个蠕虫罐头来讨论外层,但为了完整起见,我会触及这个话题。简而言之,外层甚至更复杂,尤其是在多个电镀步骤的情况下,以及使用铜还原技术来降低表面铜厚度时。有时,微带痕迹是铁砧形而不是梯形,但更常见的是它们看起来更像“台面”,借用地质学中的一个术语,顶部镀层截面几乎垂直,梯形横截面在底部;即,梯形顶部的矩形,矩形代表电镀的铜。为了对此进行建模,有些人使用 1 mil 蚀刻板作为电镀微带线。这似乎最能代表“大多数”外层,尽管它仍然错误地将横截面建模为梯形。

电镀层通常有“其他挑战”,包括可能有一个、两个甚至三个电镀通道。一些设计电镀 1 倍,最终厚度正好为 1 mil,而其他电路板则电镀 1 倍,厚度要厚得多。

图 5.“蚀刻系数”和“蚀刻因子”的拟议定义,其中 x(蚀刻系数)是 w1 和 w2 之间的差值,蚀刻系数定义为单位厚度的蚀刻系数程度。

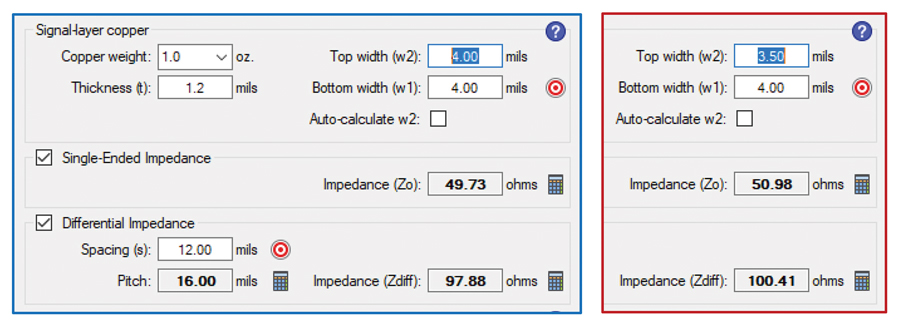

图 6.带有蓝色边框的左图采用矩形轨迹横截面。右图包括针对 50Ω 的单端传输线和针对 100Ω 的差分对的 0.5 mil 蚀刻。(使用 Z 零 Z 求解器、Mentor 的 HyperLynx 场求解器进行仿真)

阻抗影响。让我们考虑一个“平均”PCB 制造商,其中 1 盎司的带状线层具有 0.5 mil 的 etchback,并将阻抗结果与忽略 etchback 的走线进行比较。在图 6 中,带有蓝色边框的左图采用矩形走线横截面。右图包括以 50Ω 为目标的单端传输线和以 100Ω 为目标的差分对的 0.5 mil 蚀刻。如您所见,单端阻抗差为 1.25Ω,差分阻抗差约为 2.5Ω。您的设计能承受这样的差异吗?这取决于很多因素,有些是你控制的,有些是随机的。例如,您不能直接控制 Dk 变化或标称铜厚度变化,但可以将阻抗指定为 +/-10%。我们在这里显示的差异将叠加在 Dk 变化、铜厚度变化和任何其他制造变化之上。简而言之,您从一开始就放弃了欧姆,这不是好的设计实践。书目

- Gareth Parry,“蚀刻工艺和技术”,印刷电路手册,第 7 版,第 37 章,McGraw-Hill Education,Clyde Coombs 和 Happy Holden,编辑,2016 年。

- 西门子,HyperLynx SI/PI 用户指南 VX.2.8,2020 年。

- 李·里奇,《第一次正确》,第 1 卷,2003 年。